|

科盛科技研究发展部技术副理 孙嘉蓬 科盛科技研究发展部使用者经验设计师 黄智扬 |

3C产品不断朝轻量化及多功能发展,IC封装的制程技术研发也随之趋向小而精致。面对使用寿命及可靠度的需求,如何采用最佳的配置进行封装以减少缺陷发生,并提供产品最好的保护,是产业最重视的课题之一。由于影响封装质量的变因项目会随着制程复杂度增长,也使得研发阶段寻求优化方案的难度提升;此外,IC封装材料以及所使用的相关组件均价格不斐,因此在封装研发的阶段若能以透过CAE分析取代实验试误、及早找到最佳方案,便能大幅减少材料及运送等成本。

Moldex3D Studio的IC封装解决方案提供以转注成型(Transfer Molding)、成型底部填胶(Molded Underfill)、毛细底部填胶(Capillary Underfill)、灌胶(Potting)、压缩成型(Compression Molding)等方式模拟封装填料过程,并可辅以排气分析 (Venting Analysis)、金线偏移分析 (Wire Sweep Analysis)、导线架偏移分析 (Paddle Shift Analysis)、后熟化分析 (Post Mold Curing Analysis)等功能,完成更真实的模拟。以下简单说明Studio封装仿真流程。

1. 制作模型

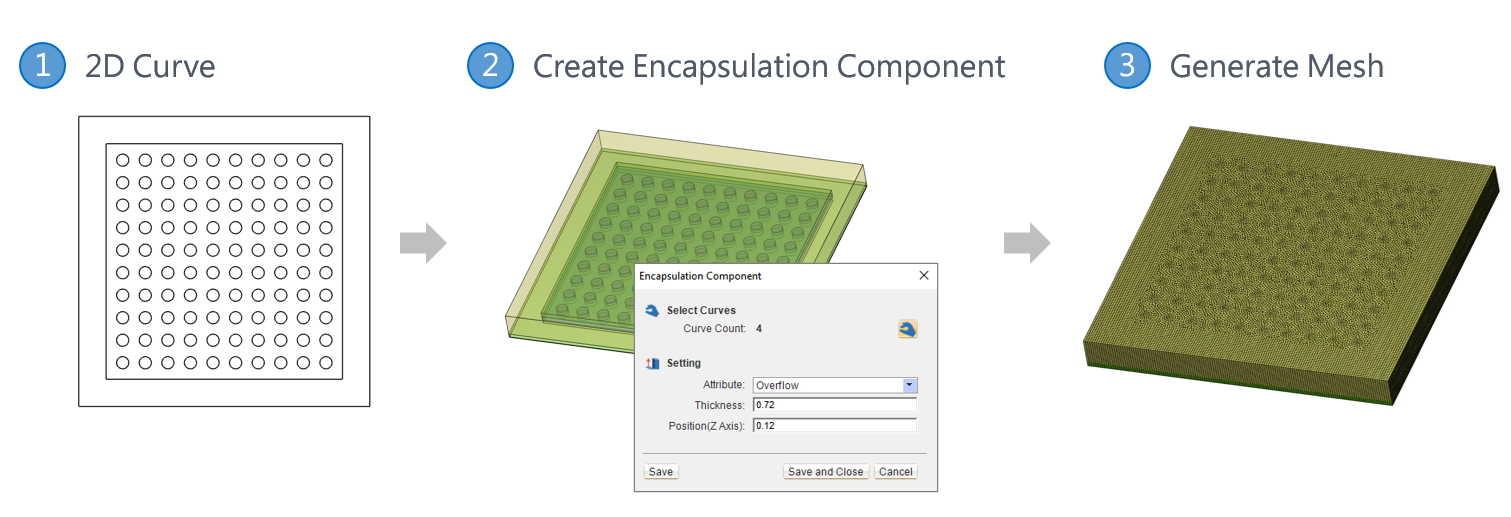

在制程类型(Molding Type)选择芯片封装(Encapsulation)(图一),接下来可直接汇入已制作完成的网格,或是使用Studio的工具建立自己的模型。使用封装组件(Encapsulation Component)精灵可以由2D曲线产生IC对象,并可指定位置及厚度,后续即可在产生网格时自动生成Hybrid网格(图二)。要注意不同分析模块需有符合的属性对象及进料类型,如压缩成型分析需有压缩区及移动面、灌胶分析需将进料路径在溢流区。

图一 制程类型选择芯片封装

图二 使用封装组件产生Hybrid网格

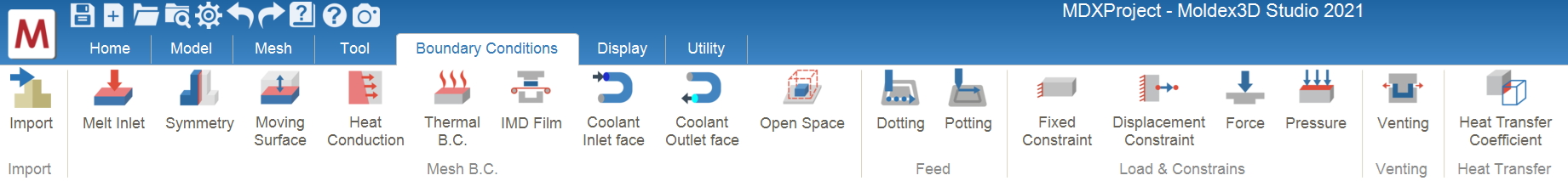

2. 边界条件设定

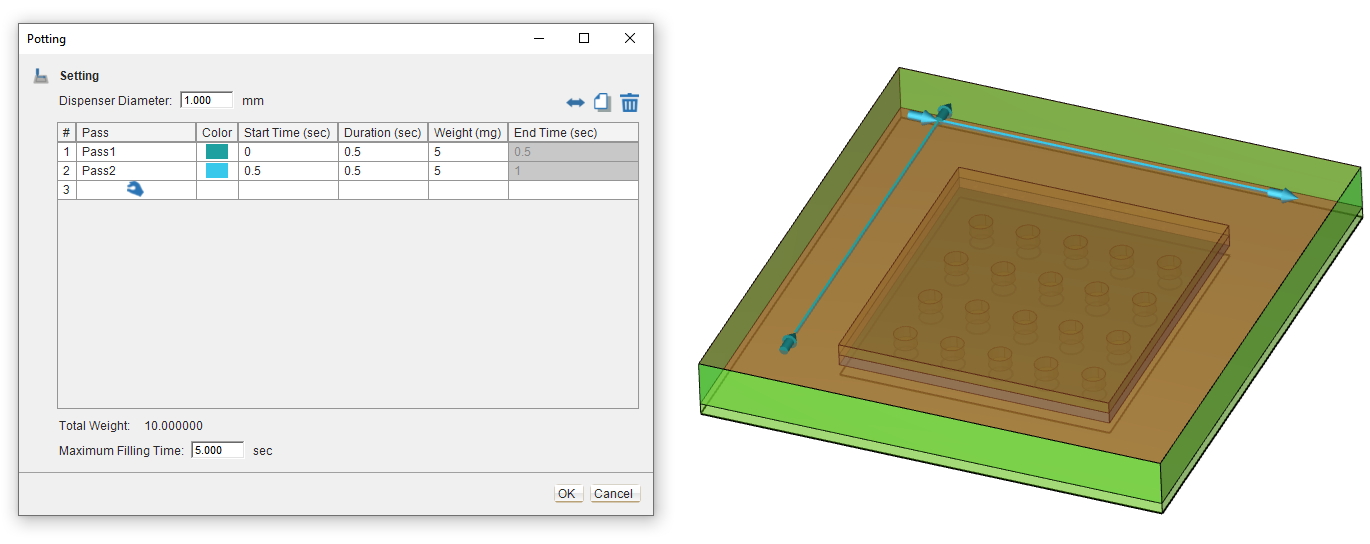

依照模拟类型,在边界条件(Boundary Condition)页签会有不同边界条件可以设定,对于毛细底部填胶分析、灌胶分析可于此设定打点式及灌胶式路径;压缩成型则可指定预填料(Charge);导线架偏移等分析需要将导线架固定面加上固定拘束边界条件。

图三 边界条件(Boundary Condition)页签

图四 灌胶路径设定

图五 导线架设定固定拘束边界条件

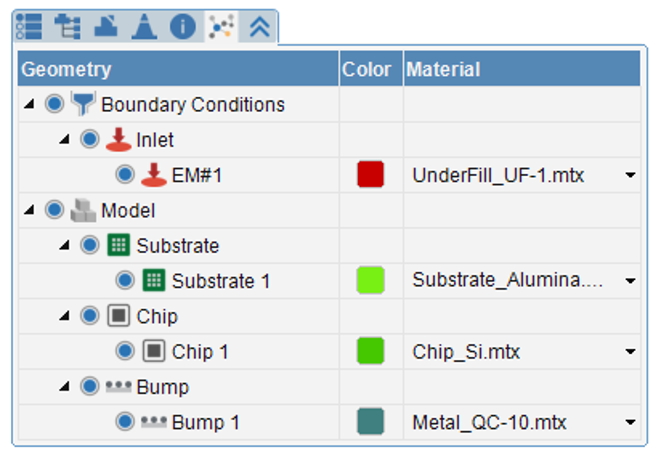

3. 材料设定

由Moldex3D材料库指定各种属性组件的材料,用户也能依照各自情况自定义材料。

图六 依照各对象属性设定材料

4. 加工条件设定

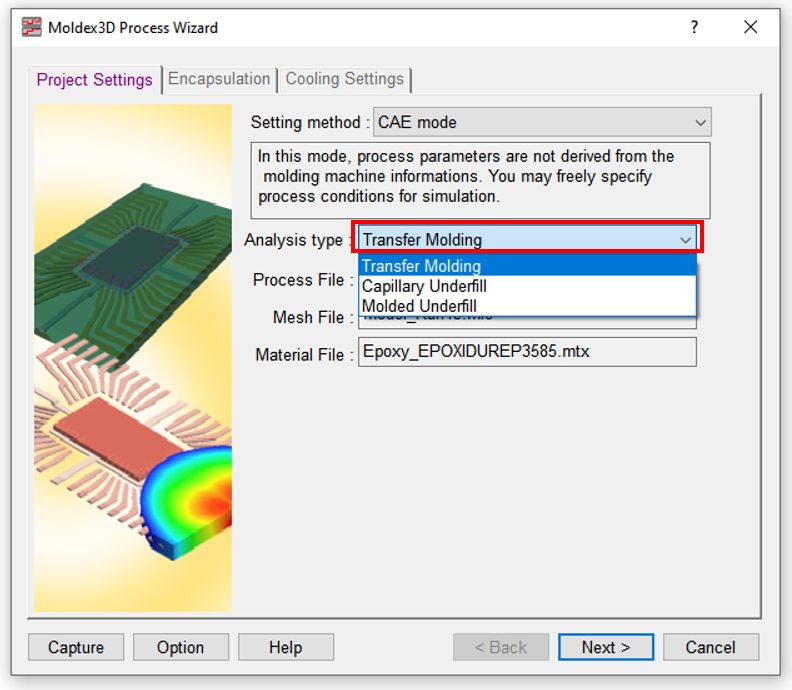

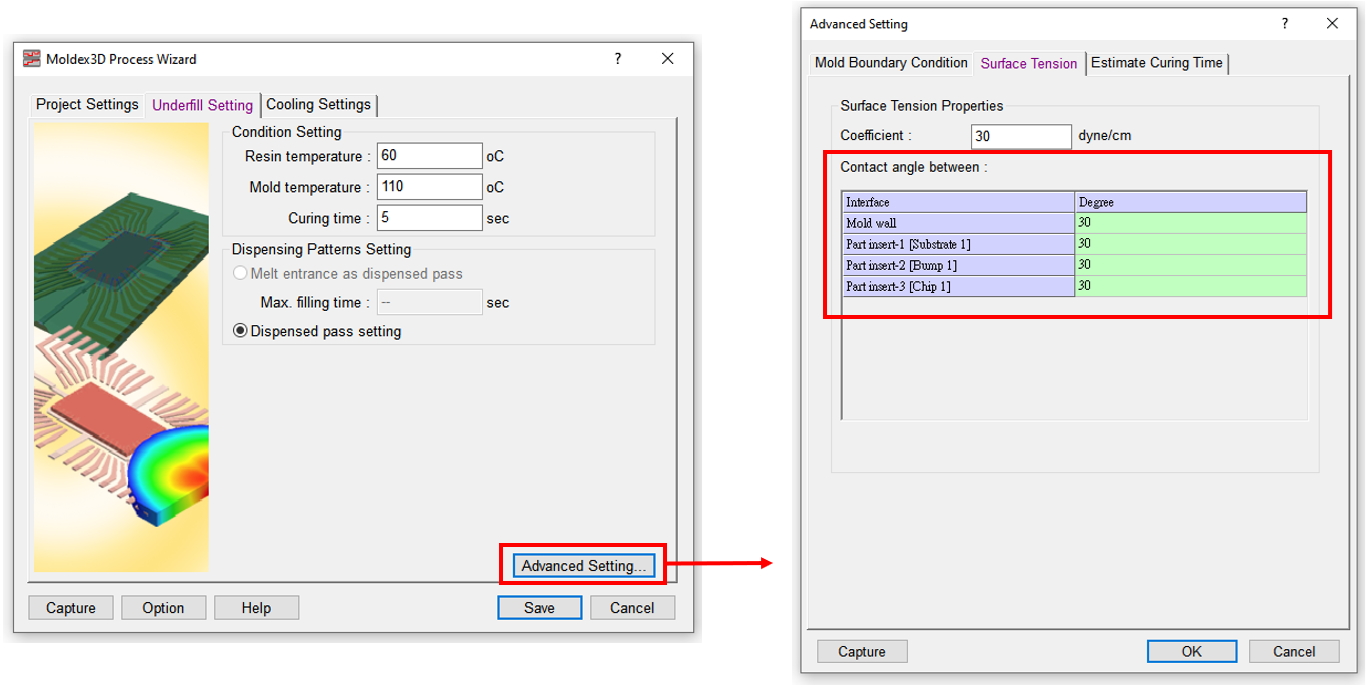

若网格进浇(Inlet)设定在环氧树脂(Epoxy)上,分析方式(Analysis Type)可选择是转注成型模块(Transfer Molding)、成型底部填胶模块(Molded Underfill)、毛细底部填胶模块(Capillary Underfill)(图七);若网格包含压缩区,分析方式可选择为压缩成型(Compression Molding)、嵌入式晶圆级封装(Embedded Wafer Level Packaging, EWLP)、非流动性底部填胶(No-Flow Underfill);若已设定点胶/打点/灌胶路径边界条件(Dispensing/Dotting/Potting BC),分析方式会自动选择并锁定。需要考虑表面张力(Surface Tension)的制程如底部充填等,可依照流动行为,在进阶设定中进行接触角设定(图八)。

图七 选择分析方式

图八 进阶设定之接触角设定

5. 分析序列

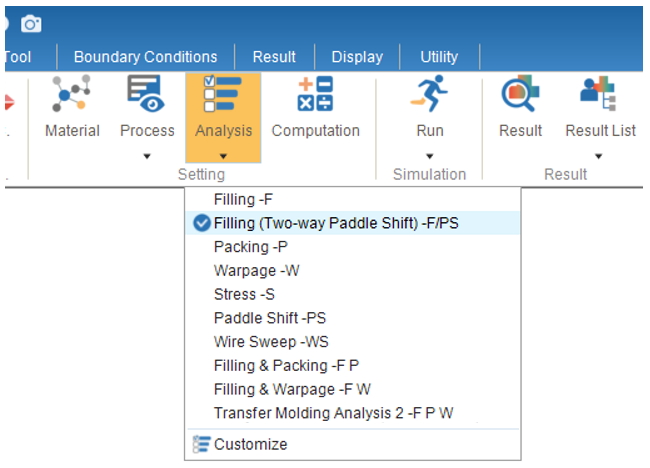

设定充填、熟化、翘曲等分析序列(图九);金线偏移分析、导线架偏移分析也需将对应的分析序列设定在充填分析之后来考虑单向流固耦合(FSI)。若指定的是以充填分析-双向导线架偏移(F/PS, Filling – Two-way Paddle Shift)取代 F+PS,则导线架偏移结果会考虑双向流固耦合(FSI)并和充填结果一起产生。

图九 分析序列设定

6. 分析设定

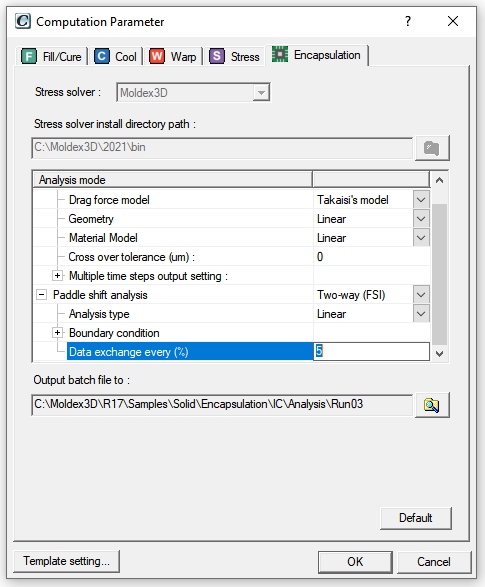

在封装(Encapsulation)页签中,可针对金线偏移分析、导线架偏移分析选择分析的应力求解器(Stress Solver),及分析所使用的计算模型;若在分析序列指定的充填-双向导线架偏移分析(F/PS),在此可以设定双向流固耦合数据交换步距(图十)。

图十 封装页签选择分析模型及指定双向流固耦合数据交换步距

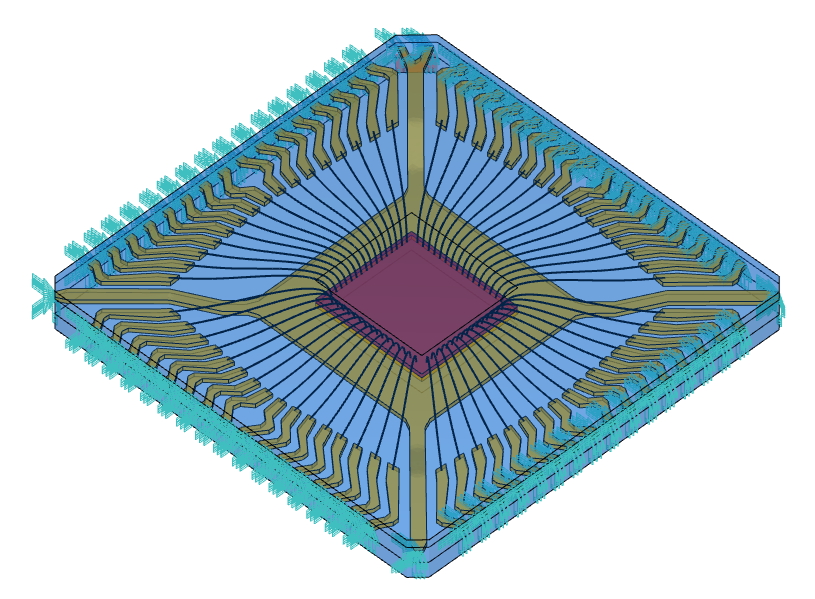

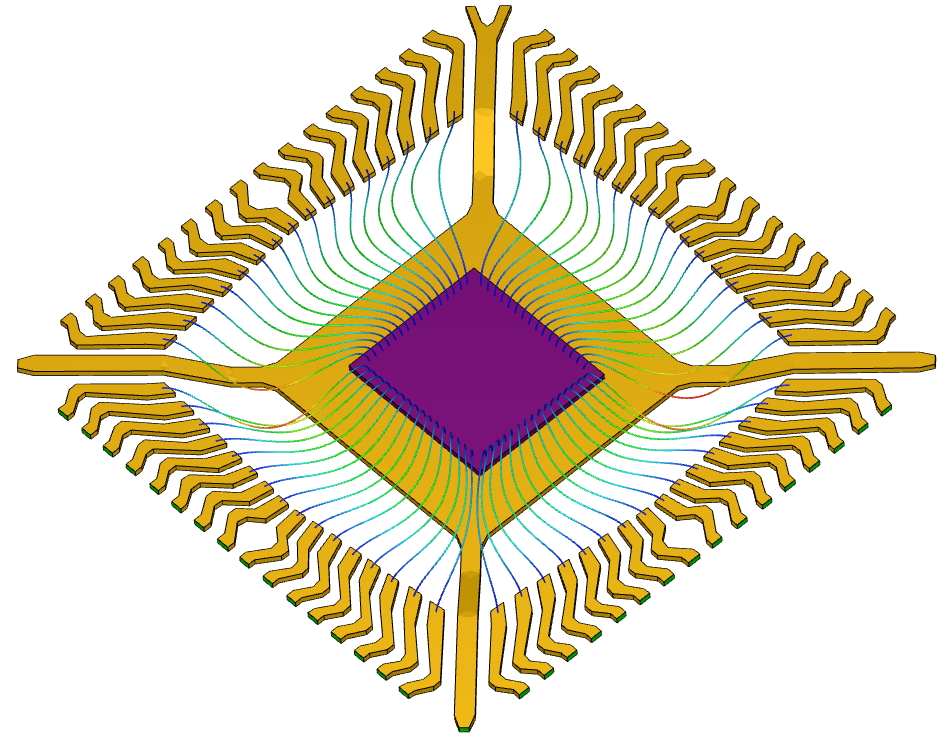

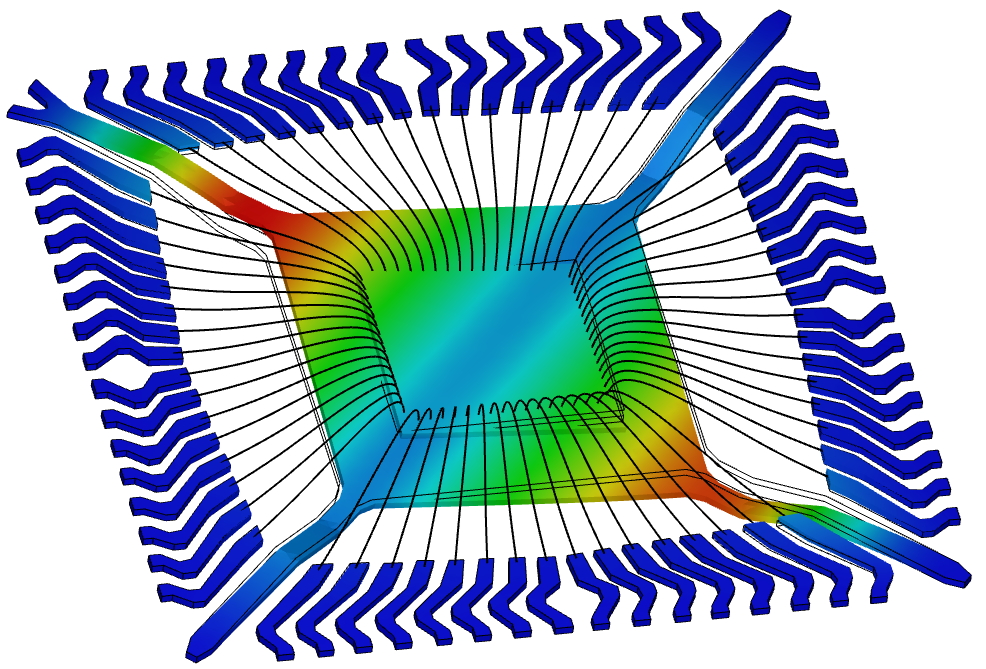

Studio封装分析模拟结果可视化呈现胶体充填/压缩过程中的流动情况及气泡产生位置(图十一)、金线偏移(图十二)、导线架偏移变形趋势(图十三)、底部充填毛细力流动行为(图十四)等。使用者可藉此修改IC设计、制程参数来避免气泡产生、金线重迭、导线架偏移量过大等缺陷产生,免去实验试误的过程,更有效率地提升IC封装设计质量。

图十一 可视化呈现胶体流动行为及气泡产生位置

图十二 金线位移搭配变形功能,显示金线变形趋势

图十三 导线架位移 – 总位移变形结果